2.2 Verilog 组合逻辑 UDP

与非门实例 组合逻辑 UDP 中,状态表规定了不同的输入组合和相对应的输出值,没有指定的任意组合输出值为 x。 一个简单的与非门 UDP 可以表...

2.1 Verilog UDP 基础知识

门级建模中介绍的内置门单元,例如 and,or , nor 等,均属于 Verilog 自带的一整套标准原语,即通常所说的内置原语。 此外,Verilog 还为用...

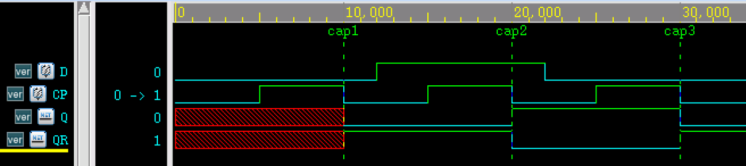

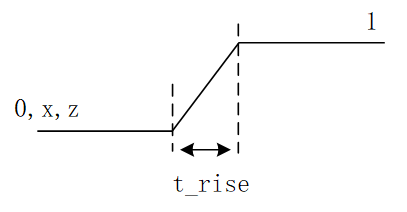

1.3 Verilog 门延迟

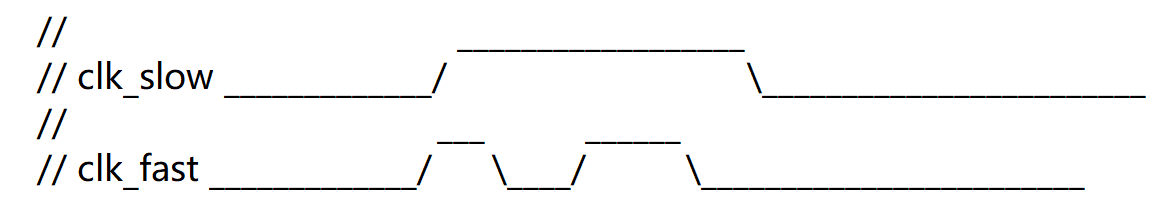

关键词: 门延迟, D 触发器 门延迟类型 前两节中所介绍的门级电路都是没有延迟的,实际门级电路都是有延迟的。 Verilog 中允许用户使用...

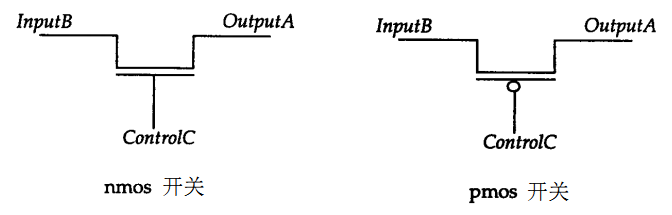

1.2 Verilog 开关级建模

关键词:MOS, CMOS, 双向开关, PAD 开关级建模是比门级建模更为低级抽象层次上的设计。在极少数情况下,设计者可能会选择使用晶体管作为设计...

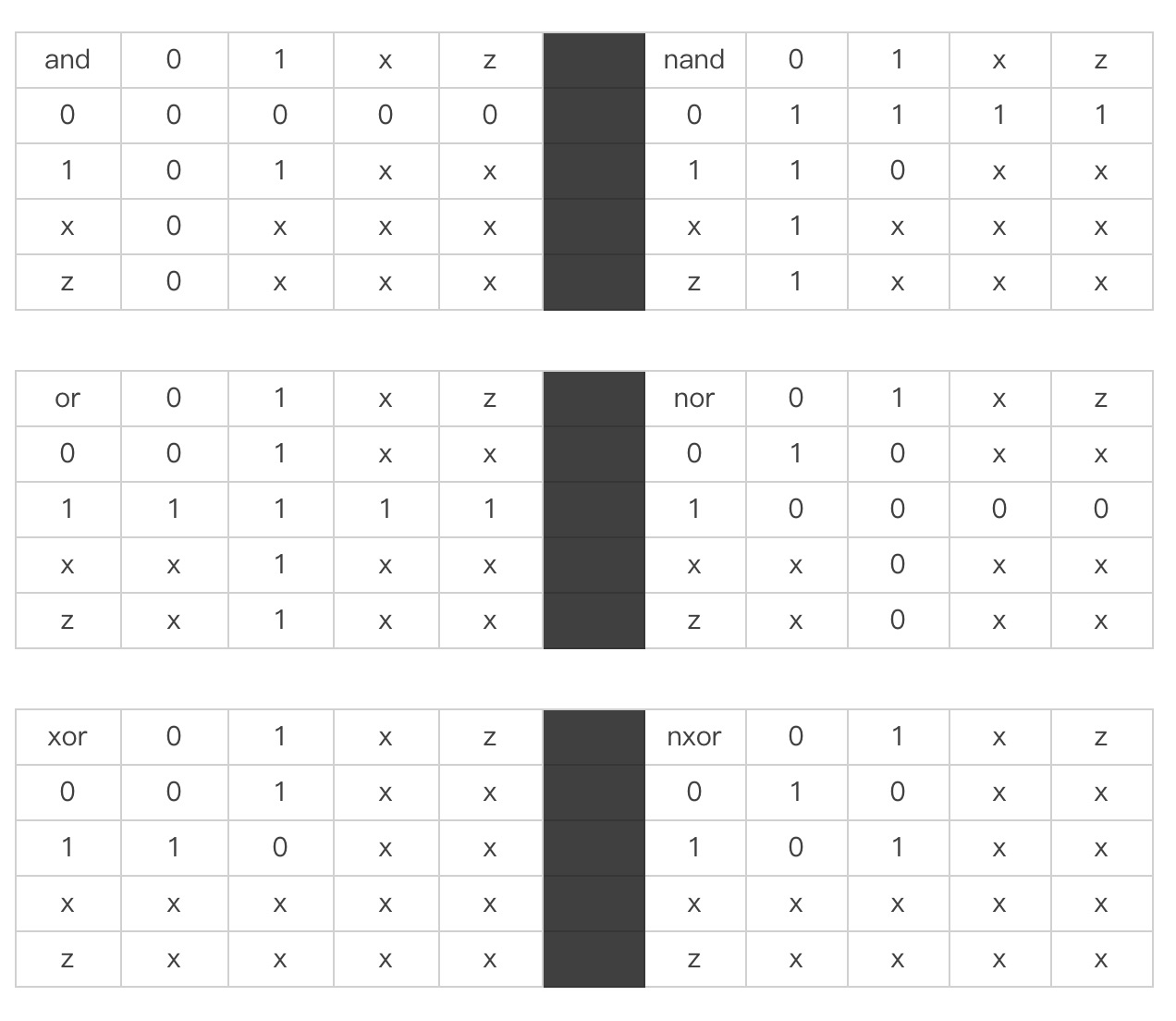

1.1 Verilog 门的类型

关键词:三态门, 上下拉, 选择器 门级建模,是使用基本的逻辑单元,例如与门,与非门等,进行更低级抽象层次上的设计。与行为级建模相比,...

0.3 Verilog 代码规范

不经意间看到几年前自己写的 FGPA 设计,代码风格勉强说的过去,但是逻辑设计方面的安全隐患比比皆是。许多初学者编写 Verilog 代码,基本都是...

0.2 Verilog 编码风格

良好的编码风格,有助于代码的阅读、调试和修改。虽然 Verilog 代码可以在保证语法正确的前提下任意编写,但是潦草的编码风格往往是一锤子买卖...

0.1 数字逻辑设计

前言 本教程主要讲述 Verilog 完成数字 IC 设计(数字集成电路设计,Digital Integrated Circuit Design) 时涉及的一些知识,更加注重数字电...