7.2 Verilog 文件操作

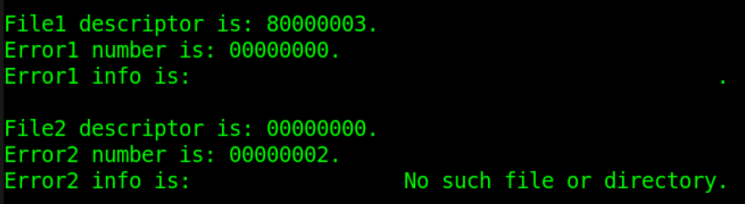

Verilog 提供了很多可以对文件进行操作的系统任务。经常使用的系统任务主要包括: 文件开、闭:$fopen, $fclose, $ferror 文件写入:$fdis...

7.1 Verilog 显示任务

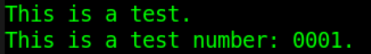

关键词:$display, $write, $strobe, $monitor Verilog 中主要用以下 4 种系统任务来显示(打印)调试信息:$display, $write, $strobe, $mon...

6.4 Verilog RTL 级低功耗设计(下)

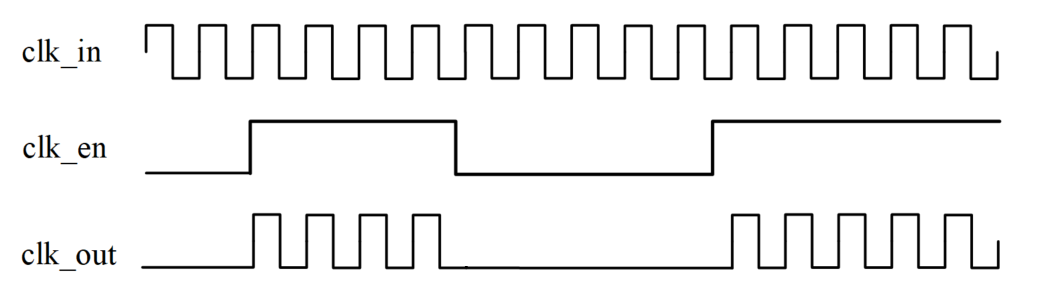

门控时钟 通常情况下,时钟树由大量的缓冲器和反相器组成。而时钟信号为设计中翻转率最高的信号,时钟树的功耗可高达整个设计功耗 30%。加入...

6.3 Verilog RTL 级低功耗设计(上)

下表显示了在数字设计的各个层次上可减少功耗的百分比。RTL 级之后,功耗的减少量已经非常有限。 设计层次改善程度系统级50% ~ 90%RTL 级20% ...

6.2 Verilog 系统级低功耗设计

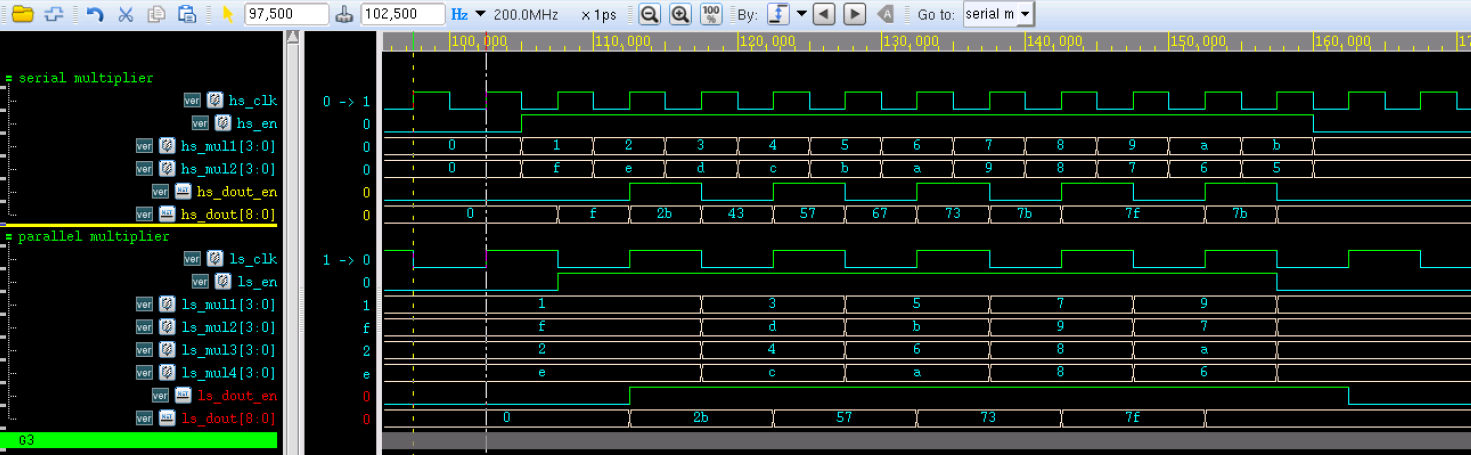

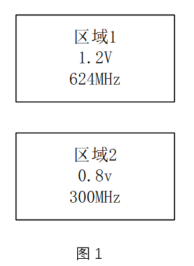

编写代码前,在系统与架构层次上制定完善低功耗方案,可以节省 50% 以上的功耗。此类低功耗设计和代码描述基本没有关系,往往由系统和架构人员...

6.1 Verilog 低功耗简介

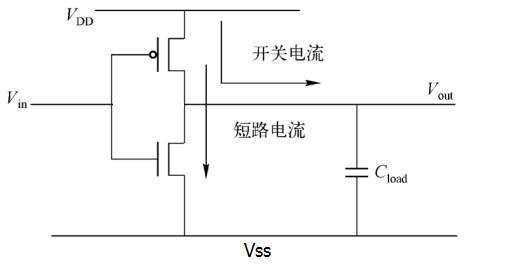

关键词:开关功耗,内部功耗,静态功耗 功耗影响 便携性 功耗越低,同等电量下电子产品工作时间越长,便携性设备的电池容量和体积设计的...

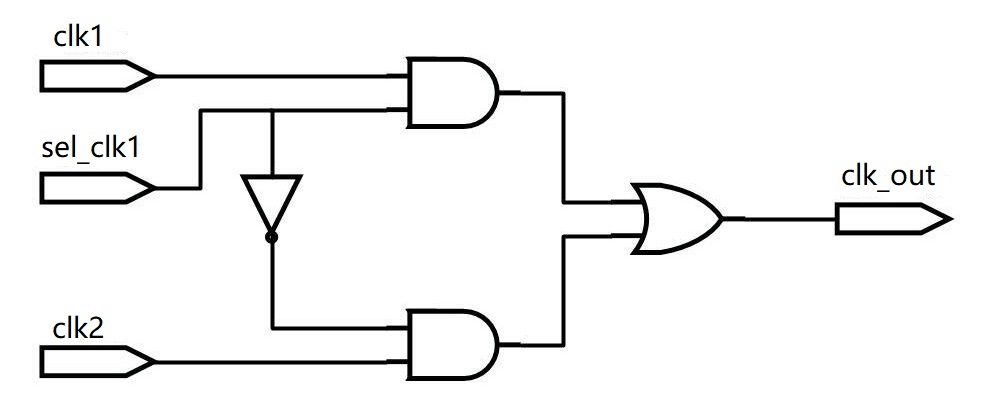

5.4 Verilog 时钟切换

随着各种应用场景的限制,芯片在运行时往往需要在不同的应用下切换不同的时钟源,例如低功耗和高性能模式就分别需要低频率和高频率的时钟。两...

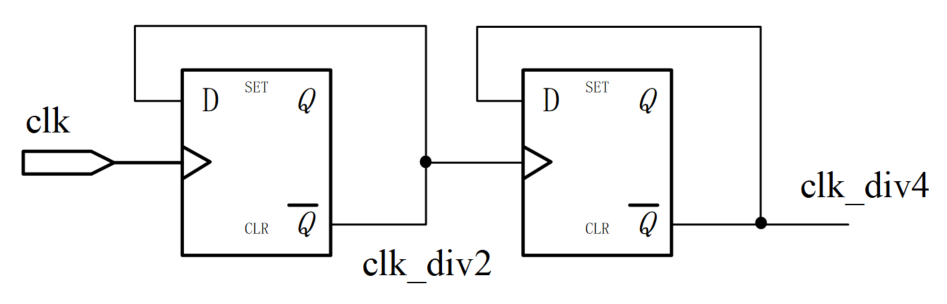

5.3 Verilog 时钟分频

关键词:偶数分频,奇数分频,半整数分频,小数分频 初学 Verilog 时许多模块都是由计数器与分频器组成的,例如 PWM 脉宽调制、频率计等。分...

5.2 Verilog 时钟简介

关键词:时钟源,时钟偏移,时钟抖动,时钟转换时间,时钟延时,时钟树,双边沿时钟 几乎稍微复杂的数字设计都离不开时钟。时钟也是所有时序...

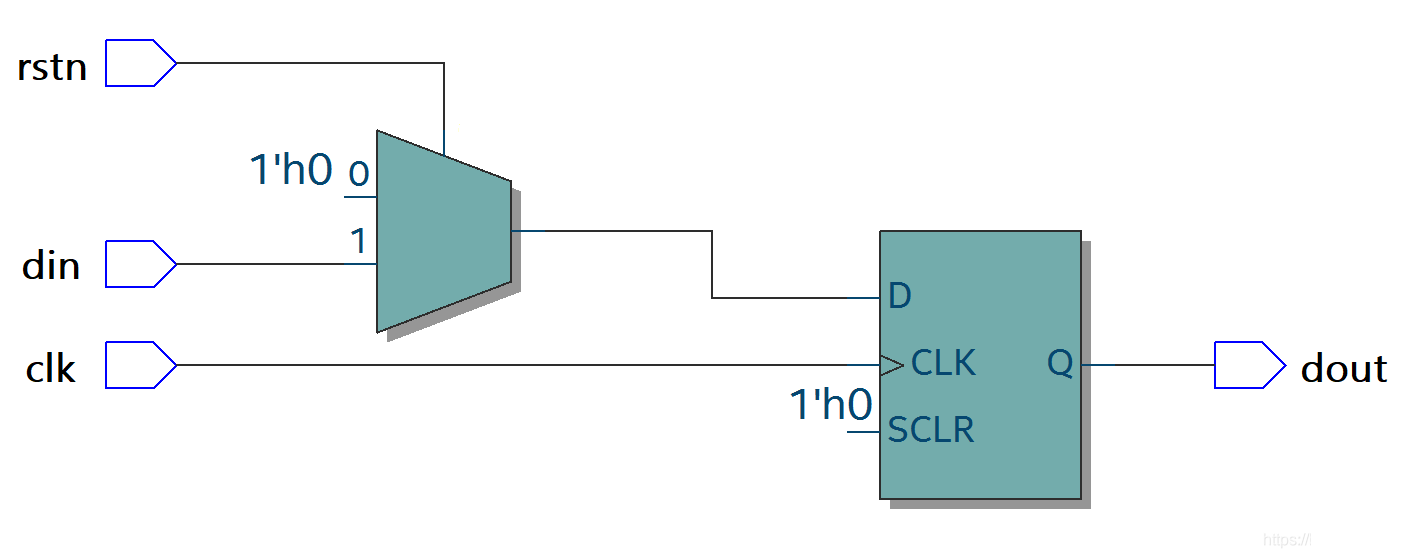

5.1 Verilog 复位简介

关键词: 同步复位, 异步复位 为确保系统上电后有一个明确、稳定的初始状态,或系统运行状态紊乱时可以恢复到正常的初始状态,数字系统设计...