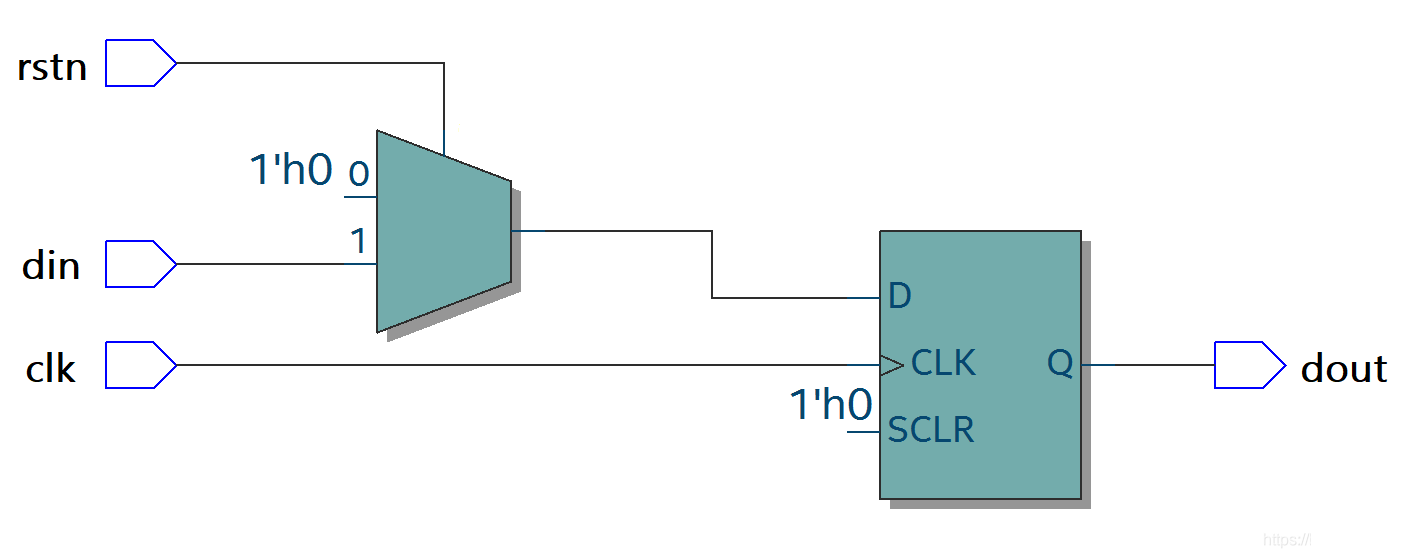

5.1 Verilog 复位简介

关键词: 同步复位, 异步复位 为确保系统上电后有一个明确、稳定的初始状态,或系统运行状态紊乱时可以恢复到正常的初始状态,数字系统设计...

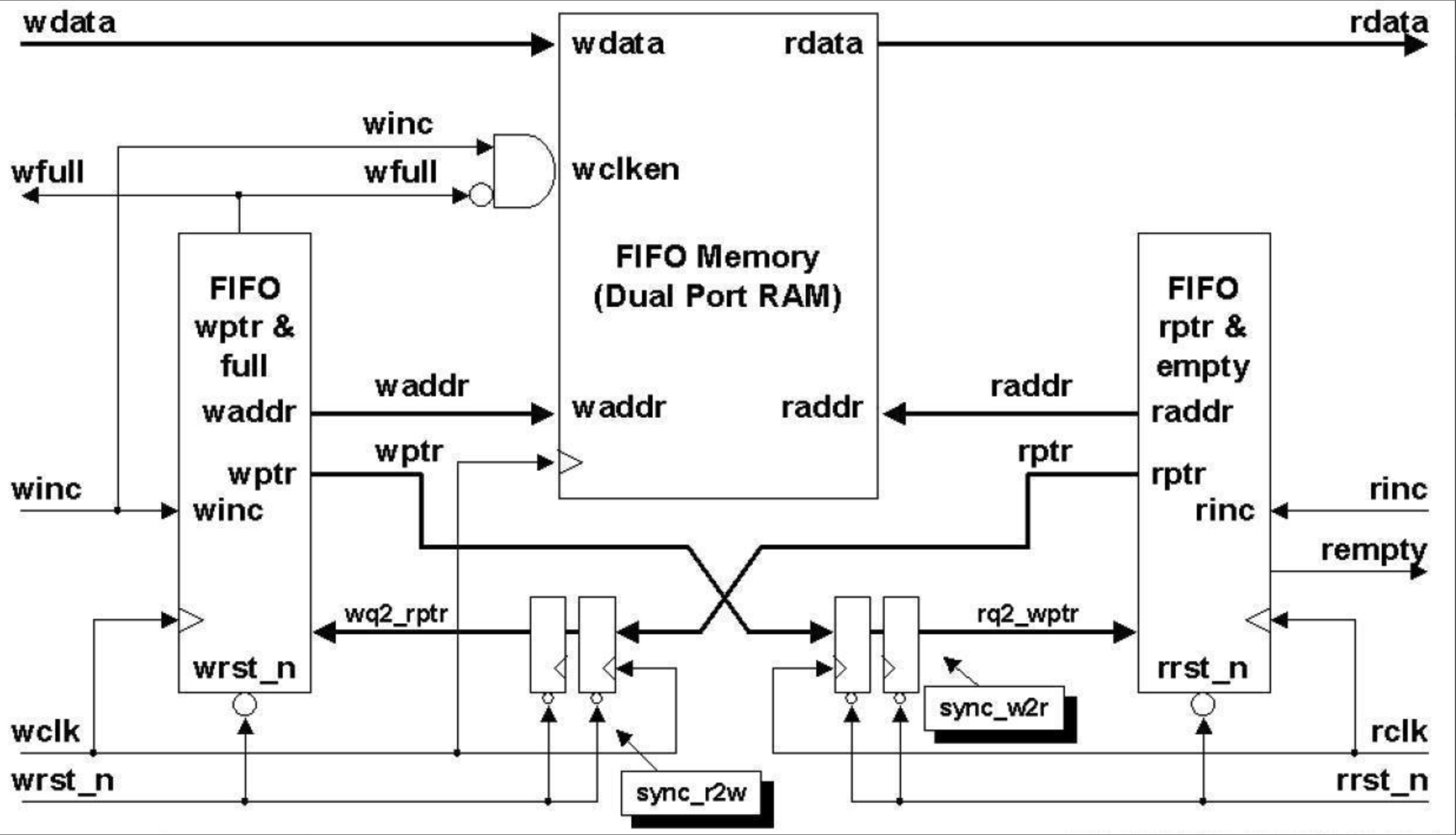

4.4 Verilog FIFO 设计

FIFO(First In First Out)是异步数据传输时经常使用的存储器。该存储器的特点是数据先进先出(后进后出)。其实,多位宽数据的异步传输问题...

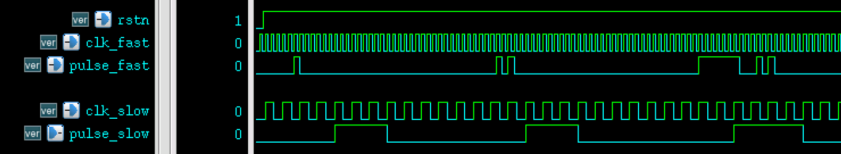

4.3 Verilog 跨时钟域传输:快到慢

信号从快时钟域传输到慢时钟域来时,需要根据信号的特点来进行同步处理。对于单 bit 信号,一般可按电平信号和脉冲信号来区分。 电平信号同...

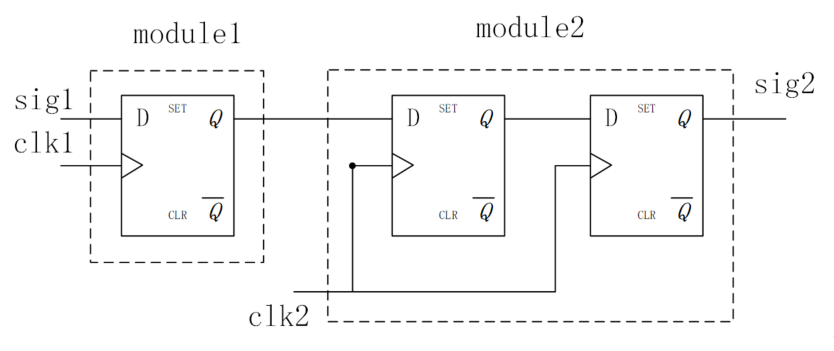

4.2 Verilog 跨时钟域传输:慢到快

理论上讲,快时钟域的信号总会采集到慢时钟域传输来的信号,如果存在异步可能会导致采样数据出错,所以需要进行同步处理。此类同步处理相对简...

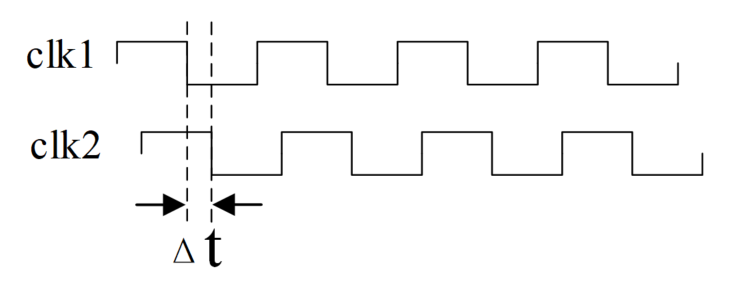

4.1 Verilog 同步与异步

关键词: 同步,异步 由第 3 章可知,当触发器输入端的数据和触发器的时钟不相关时,很容易导致电路时序不满足。本章主要解决模块间可导致时...

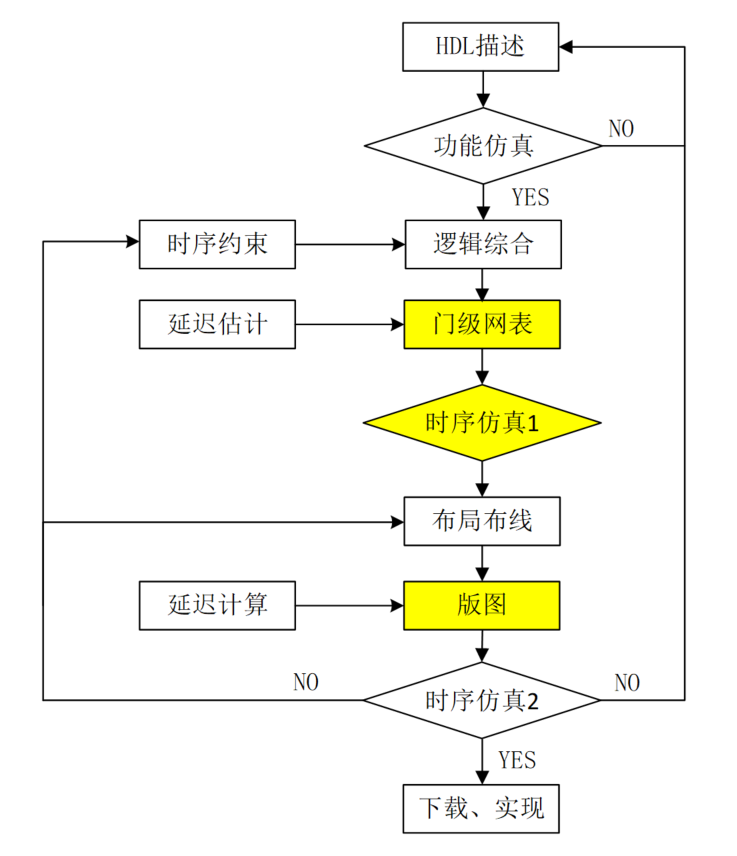

3.5 Verilog 延迟反标注

关键词: 延迟反标注, SDF 延迟反标注是设计者根据单元库工艺、门级网表、版图中的电容电阻等信息,借助数字设计工具将延迟信息标注到门级网...

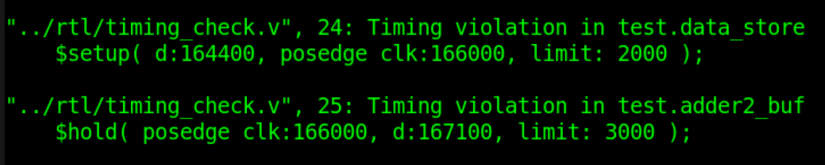

3.4 Verilog 时序检查

关键词: setup hold recovery removal width period 指定路径延迟,目的是让仿真的时序更加接近实际数字电路的时序。利用时序约束对数字设计...

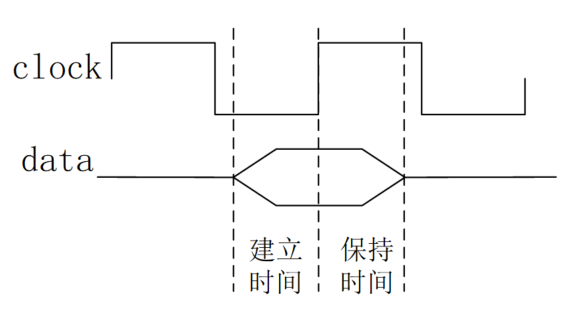

3.3 Verilog 建立时间和保持时间

关键词: 建立时间, 保持时间 对于数字系统而言,建立时间(setup time)和保持时间(hold time)是数字电路时序的基础。数字电路系统的稳定...

3.2 Verilog specify 块语句

关键词: specify, 路径延迟 路径延迟用关键字 specify 和 endspecify 描述,关键字之间组成 specify 块语句。 specify 是模块中独立的一部...

3.1 Verilog 延迟模型

关键词: 分布延迟, 集总延迟, 路径延迟 之前大部分仿真都是验证数字电路功能的正确性,信号传输都是理想的,没有延迟。但是实际逻辑元器件...