CSS 导航栏图标

本章节我们将学习如何使用 CSS 创建导航栏图标。 图标资源用的是 Font Awesome4.7 版本的图标。 Font Awesome 图标教程可以参考:Font Awes...

9.2 Verilog 可综合性设计

Verilog 主要用于数字电路设计的描述,但不是所有的描述方式都可以被综合成实际的硬件电路。例如一些用于仿真验证的关键字,属于仿真验证语言...

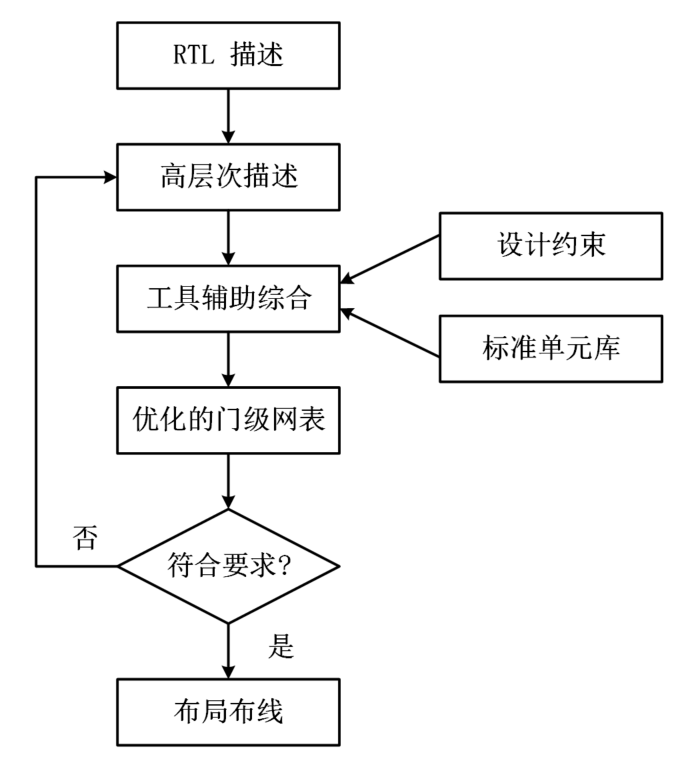

9.1 Verilog 逻辑综合

本教程经常有提及综合这个词语。或者说有些逻辑不能综合成实际电路,或者说有些逻辑设计综合后的电路会有一些安全隐患。本章就简单介绍下逻辑...

8.5 Verilog ACC 子程序列表

为保证子程序的原汁原味,避免拉跨拙劣的翻译水平,所有子程序列表均保留英文说明。这里也没有对所有的子程序都进行验证,由于版本或抄写问题...

8.4 Verilog ACC 子程序

功能特性 ACC 子程序主要完成的功能有: 从内部数据结构中读取特定对象的相关信息 把特定对象的相关信息写入内部数据结构中 ACC 子程序...

8.3 Verilog TF 子程序列表

为保证子程序的原汁原味,避免拉跨拙劣的翻译水平,所有子程序列表均保留英文说明。建议使用时再仔细研究对应类型的子程序。这里也没有对所有...

8.2 Verilog TF 子程序

功能特性 TF (task/function) 子程序主要用于 Verilog 与用户 C 程序边界的两个方向上的数据传输。 TF 子程序总是以 tf_ 为前缀,定义在头文...

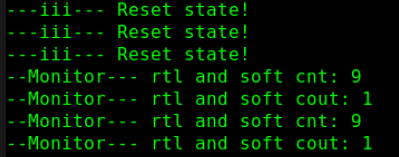

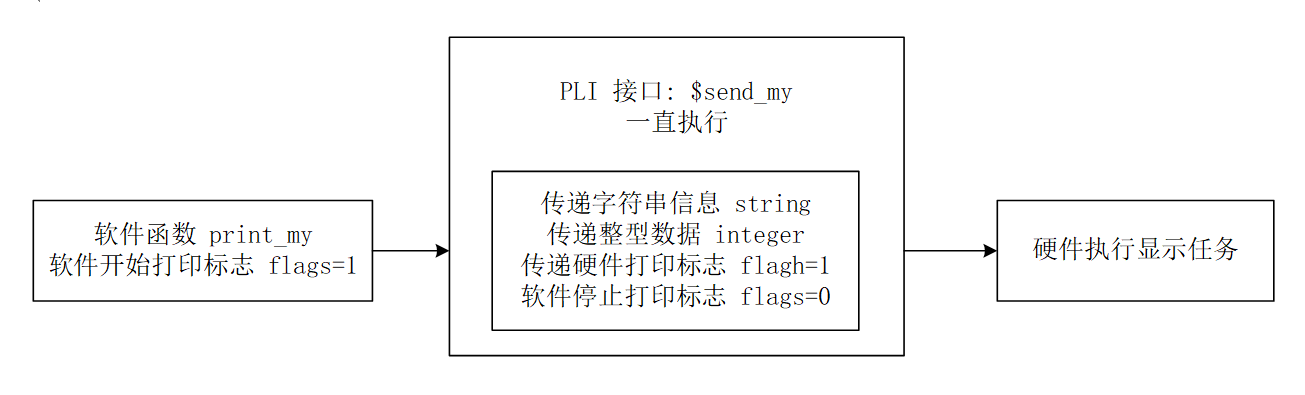

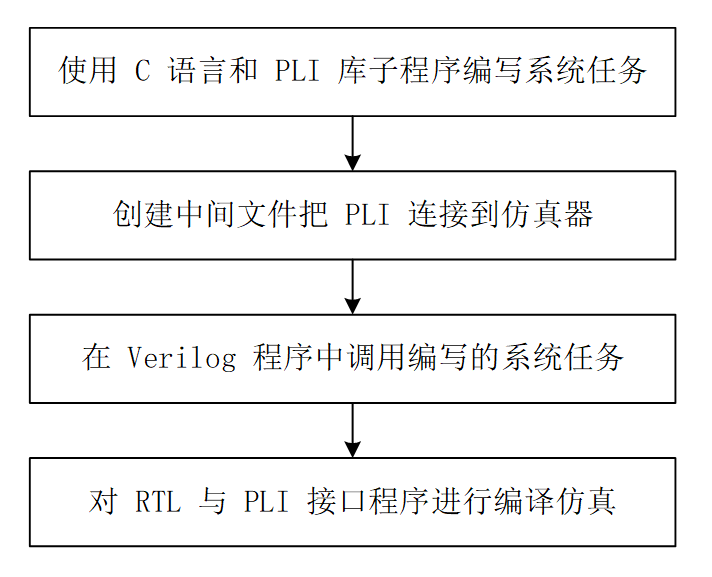

8.1 Verilog PLI 简介

进行数字设计时,经常会遇到特殊的情况,Verilog 中的任务和函数已经不能满足仿真需求,需要自定义一些系统任务和函数。编程语言接口(PLI, P...

7.5 Verilog 其他系统任务

仿真控制:$finish, $stop 系统任务调用格式任务描述退出仿真$finish( type ) ;结束仿真,参数 type 可选择退出仿真时是否打印信息type=0: ...

7.4 Verilog 实数整数转换

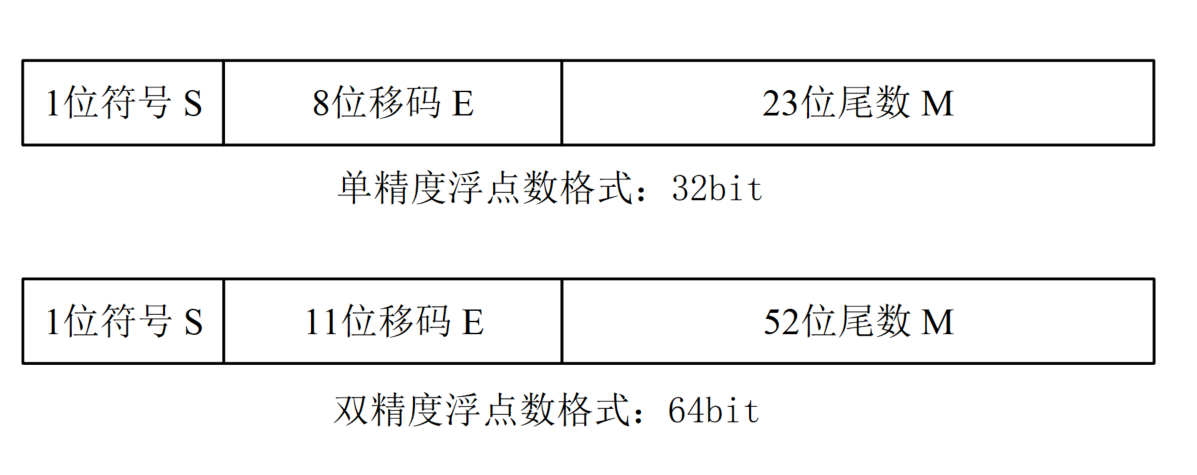

关键词 :定点数, 浮点数, $realtobits, $bitstoreal 本节主要介绍实数与整数间相互转换的函数:$realtobits, $bitstoreal,同时说明下 real ...