Python2 与 Python3 print 不换行

本文主要介绍在 Python2 与 Python3 下 print 实现不换行的效果。 Python 3.x 在 Python 3.x 中,我们可以在 print() 函数中添加 end="" 参...

JavaScript/CSS 表格排序功能

本章节我们将学习如何使用 JS/CSS 实现表格排序功能。 先看下效果如下,点击按钮实现排序(按字母升序排序,居于 Name 字段): 排序...

JavaScript/CSS 列表排序功能

本章节我们将学习如何使用 JS/CSS 实现列表排序功能。 先看下效果如下,点击按钮实现排序: 基础 HTML 代码 实例 <ul id="id...

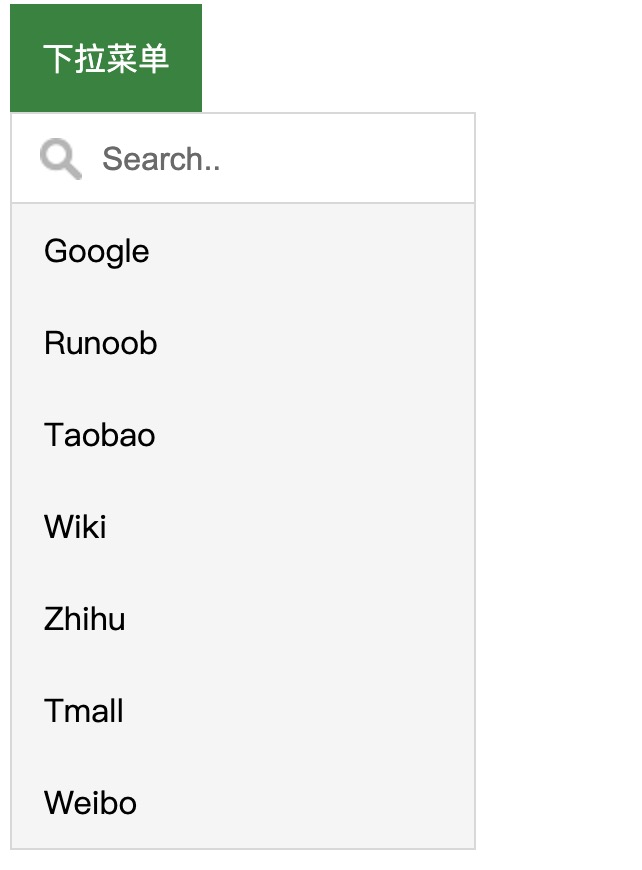

JavaScript/CSS 下拉菜单搜索功能

本章节我们将学习如何使用 JS/CSS 实现下拉菜单搜索或过滤功能。 先看下效果如下: 查看在线实例:https://c.runoob.com/codedemo/6229/...

JavaScript/CSS 表格搜索功能

本章节我们将学习如何使用 JS/CSS 实现表格搜索或过滤功能。 先看下效果如下: 查看在线实例:https://www.jyshare.com/codedemo/6228/ ...

JavaScript/CSS 列表搜索功能

本章节我们将学习如何使用 JS/CSS 实现列表搜索或过滤功能。 先看下效果如下: 查看在线实例:https://c.runoob.com/codedemo/6227/ 基...

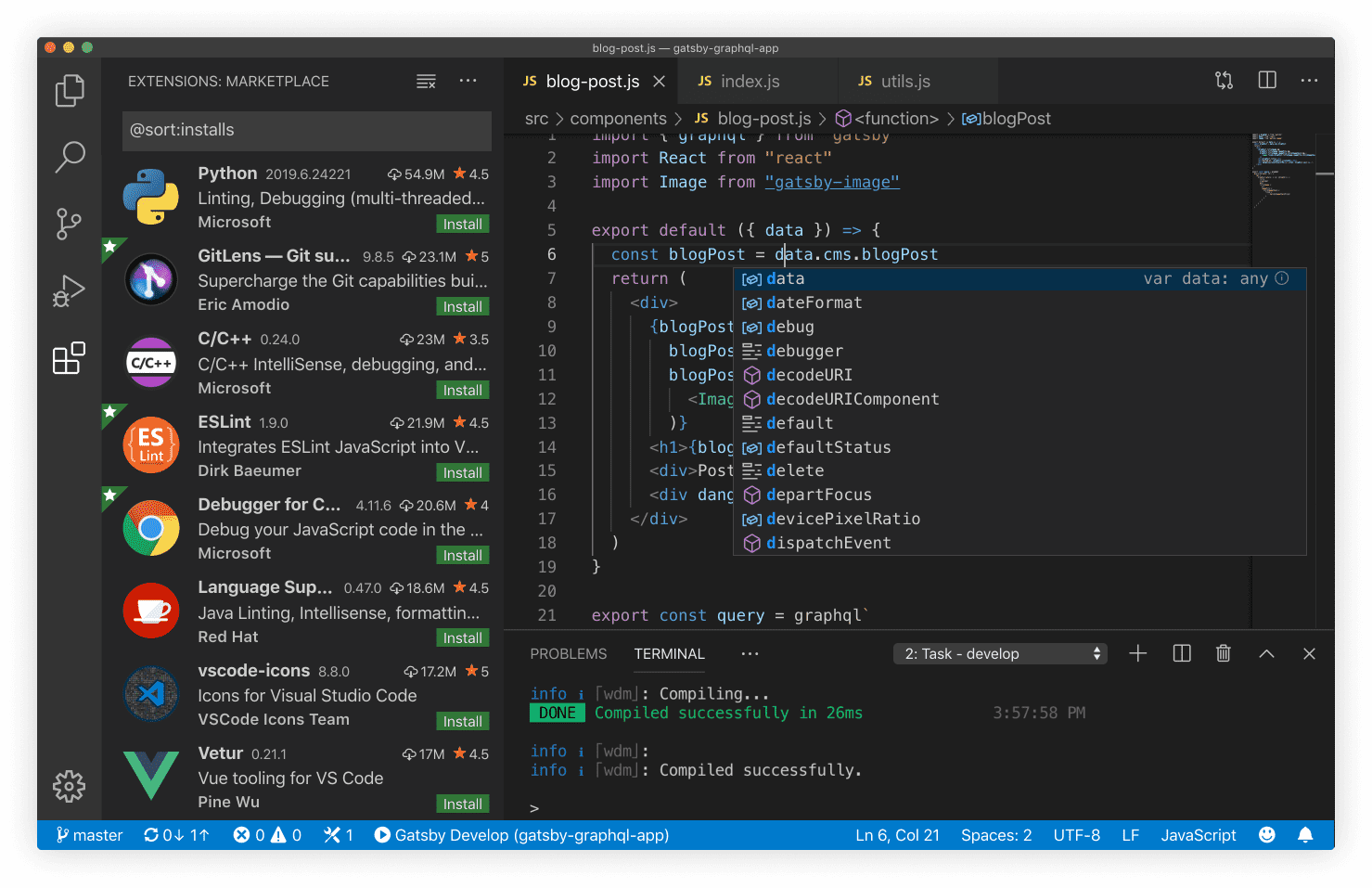

VScode 入门教程

VSCode(全称:Visual Studio Code)是一款由微软开发且跨平台的免费源代码编辑器。该软件支持语法高亮、代码自动补全(又称 IntelliSense)、...

JavaScript/CSS 实现手风琴/折叠效果

本章节我们将学习如何使用 JS/CSS 实现手风琴折叠效果。 先看下效果如下: 基础 HTML 代码 实例 <button class="accordion&quo...

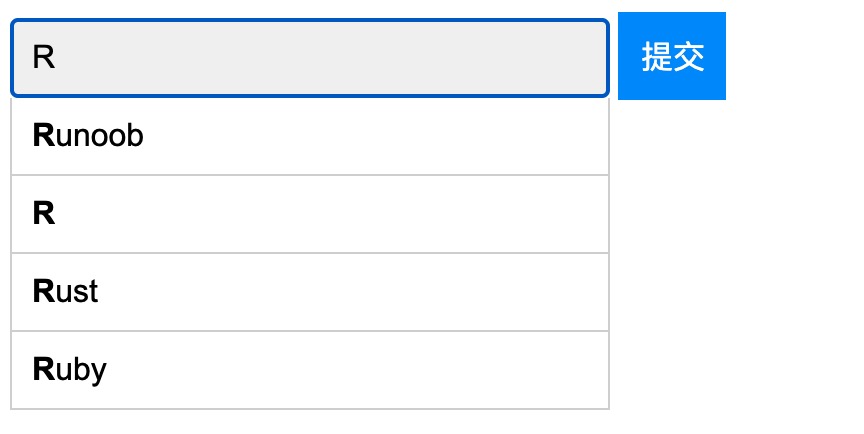

JavaScript 实现搜索框联想功能(autocomplete)

本章节我们将学习如何使用 JS/CSS 实现搜索框联想功能。 先看下效果如下: 查看在线实例:https://c.runoob.com/codedemo/6190 基础 HT...

CSS 创建搜索框

本章节我们将学习如何使用 CSS 创建搜索框。 图标资源用的是 Font Awesome4.7 版本的图标。 Font Awesome 图标教程可以参考:Font Awesome ...