关键词:三态门, 上下拉, 选择器

门级建模,是使用基本的逻辑单元,例如与门,与非门等,进行更低级抽象层次上的设计。与行为级建模相比,门级建模更注重硬件的实现方法,即通过连接一些基本门电路去实现多种逻辑功能。虽然行为级建模最后也会被综合成基本的门级电路网络,但对于复杂的设计来说,行为级建模的效率远远高于门级建模。所以目前 Verilog 大多数用于描述数字设计的行为级层次(RTL),一般只注重设计实现的算法或流程,而不用特别关心具体的硬件实现方式。

有些设计,例如门控时钟,就需要使用基本门单元,来增加电路的可控性与可靠性。

多输入门

多输入门只有单个输出,有单个或多个输入端。Verilog 内置多输入门如下:

and(与门) nand(与非门) or(或门) nor(或非门) xor(异或门) xnor(同或门)

使用基本的逻辑门单元去实现一些简单的逻辑功能时,使用模块例化的方式即可。

门级单元第一个端口是输出,后面端口是输入,例化调用时需要注意。

门级单元实例调用的时候,也可以不指定实例的名字,这为代码编写提供了方便。

当输入端口超过 2 个时,只需将输入信号在端口列表中继续排列即可,Verilog 可自动识别。

实例

and a1 (OUTX, IN1, IN2) ;

nand na1 (OUTX1, IN1, IN2) ;

or or1 (OUTY, IN1, IN2) ;

nor nor1 (OUTY1, IN1, IN2) ;

//3 input

xor xor1 (OUTZ, IN1, IN2, IN3) ;

//no instantiation name

xnor (OUTZ1, IN1, IN2) ;

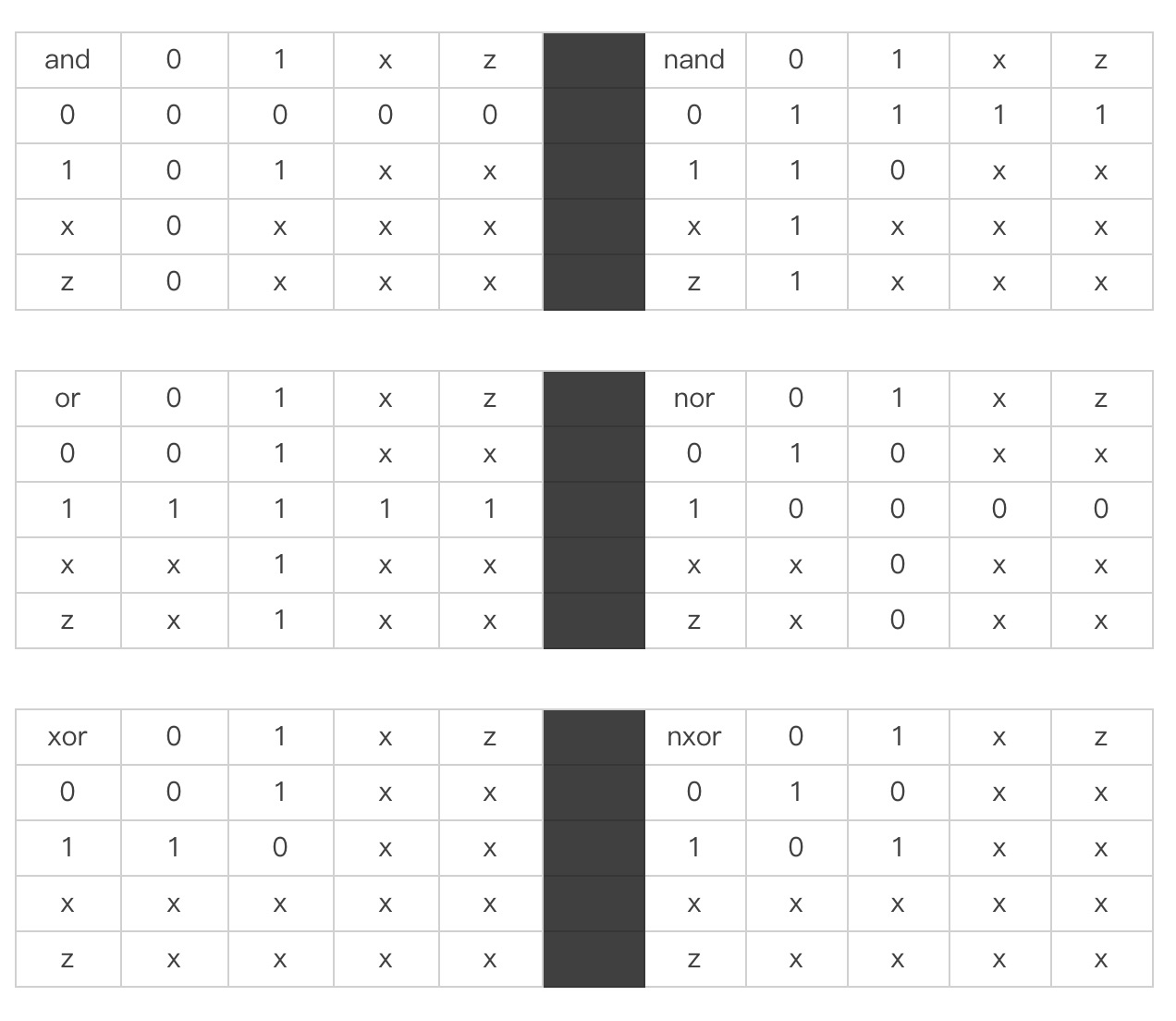

多输入门的真值表如下,注意输出不会出现 Z。

多输出门

多输出门只有单个输入,有单个或多个输出端,又可称之为 buffer,起缓冲、延时作用。

内置多输入门如下:

buf(缓冲器) not(非门)

和多输入门类似,可以使用模块例化的方式对多输出门进行调用。

门级单元第一个端口是输出,最后一个端口是输入。当输出端口超过 1 个时,需将输出信号在最后一个输入端口前排列。

例化时也可以不指定实例的名字。

实例

buf buf1 (OUTX2, IN1) ;

//2 output

buf buf2 (OUTY2, OUTY3, IN2) ;

//no instantiation name

not (OUTZ3, IN3) ;

多输出门的真值表如下,注意输出不会出现 Z。

| buf | 0 | 1 | x | z | not | 0 | 1 | x | z | |

|---|---|---|---|---|---|---|---|---|---|---|

| 输出 | 0 | 1 | x | x | 输出 | 1 | 0 | x | x |

三态门

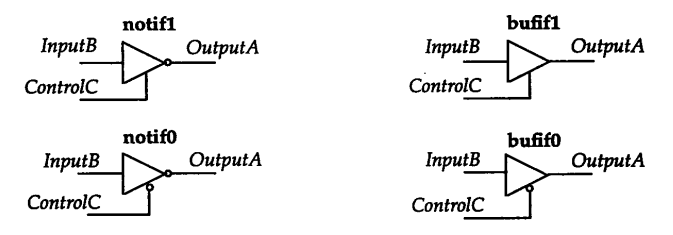

Verilog 中还提供了 4 个带有控制端的 buffer 门单元,称为三态门。只有当控制信号有效时,数据才能正常传递,否则输出为高阻抗状态 Z。

4 个三态门名称及符号如下:

例化时,三态门第一个端口为输出端,第二个端口为数据输入端,第三个端口为控制输入端。例化时信号排列顺序要一致。

三态门不支持输出端口超过 1 个,但例化时可以不指定实例的名字。

实例

bufif1 buf1 (OUTX, IN1, CTRL1) ;

bufif0 buf2 (OUTY, IN1, CTRL2) ;

notif1 buf3 (OUTZ, IN1, CTRL3) ;

//no instantiation name

notif0 (OUTX1, IN1, CTRL4) ;

三态门的真值表如下。

表中有些为可选项,例如,1/z 表明,根据输入端和控制端的信号强度,输出端既可能为 1,也可能为 z。

| bufif1 | 控制端 | bufif0 | 控制端 | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | x | z | 0 | 1 | x | z | |||

| 0 | z | 0 | 0/z | 0/z | 0 | 0 | z | 0/z | 0/z | |

| 1 | z | 1 | 1/z | 1/z | 1 | 1 | z | 1/z | 1/z | |

| x | z | x | x | x | x | x | z | x | x | |

| z | z | x | x | x | z | x | z | x | x |

| notif1 | 控制端 | notif0 | 控制端 | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | x | z | 0 | 1 | x | z | |||

| 0 | z | 1 | 1/z | 1/z | 0 | 1 | z | 1/z | 1/z | |

| 1 | z | 0 | 0/z | 0/z | 1 | 0 | z | 0/z | 0/z | |

| x | z | x | x | x | x | x | z | x | x | |

| z | z | x | x | x | z | x | z | x | x |

利用三态门实现可配置输入输出 PAD 功能的例程,可参见该教程《1.2 开关级建模》一节。

利用三态门实现可配置上下拉 PAD 功能的例程,可参见《Verilog 教程》的《5.1 Verilog 模块与端口》一章。

上下拉电阻

上拉是将不确定的信号通过一个电阻钳制在一个高电平。

下拉是将不确定的信号通过一个电阻与地相连,固定在低电平。

模块端口的上拉或下拉电阻,具有限流、提高驱动能力、防静电等作用,可以有效保护电路。

当信号方向为输入且没有输入信号(高阻态)时,上拉会将该信号的逻辑值置为 1,下拉会将该信号的逻辑值置为 0。

Verilog 提供了为信号设置上、下拉电阻的逻辑门单元,多用于模块端口信号。

此类门单元没有输入,只有输出。关键字如下:

pullup(设置上拉) pulldown(设置下拉)

例化调用时,只需填写需要设置上下拉电阻的信号即可。

实例的名字也可以不指定。

pullup p1 (IN1); pulldown (OUTX);

此处设置上下拉电阻后就不能再更改。在《Verilog 教程》的《5.1 Verilog 模块与端口》一章中,利用三态门 buffer 实现了可配置上下拉 PAD 功能的实例,欢迎参考。

4 选 1 多路选择器

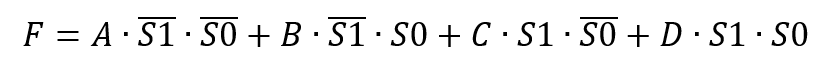

下面对比四选一选择的实现方式,来说明门级建模较行为级建模的繁琐性。

输入为 A、B、C、D,输出为 F,选择信号为 SEL1、SEL0,则 4 路选择器的表达式为:

门级建模如下:

实例

input A, B, C, D ,

input S0, S1,

output F );

//reversing

wire S0R, S1R ;

not (S0R, S0) ;

not (S1R, S1) ;

//logic and

wire AAND, BAND, CAND, DAND ;

and (AAND, A, S1R, S0R);

and (BAND, B, S1R, S0);

and (CAND, C, S1, S0R);

and (DAND, D, S1, S0);

//logic or

or (F, AAND, BAND, CAND, DAND) ;

endmodule

行为级建模如下:

实例

input A, B, C, D ,

input S0, S1,

output F );

assign F = {S1, S0} == 2'b00 ? A :

{S1, S0} == 2'b01 ? B :

{S1, S0} == 2'b10 ? C :

{S1, S0} == 2'b11 ? D : 0 ;

endmodule

虽然行为级建模综合后的结果可能与门级建模一致,但是在设计时,显然行为级建模有更好的可读性、简洁性。

点我分享笔记